Aetherling

Type-Directed Scheduling of Streaming Accelerators

David Durst,

Matthew Feldman,

Dillon Huff,

David Akeley,

Ross Daly,

Gilbert Louis Bernstein,

Marco Patrignani,

Kayvon Fatahalian,

Pat Hanrahan

Programming Language Design and Implementation (PLDI), 2020

Abstract

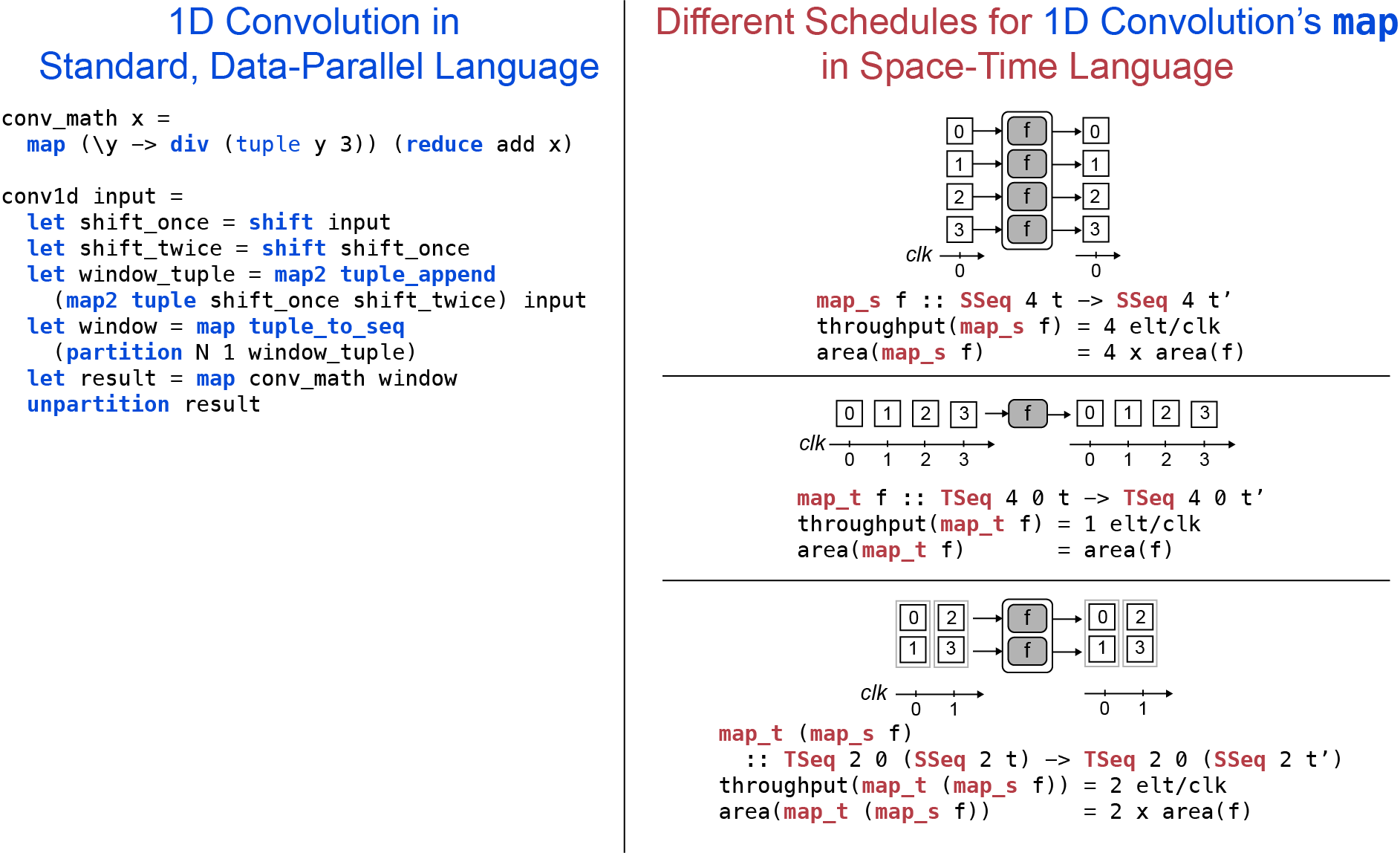

Designing efficient, application-specialized

hardware accelerators requires assessing trade-offs

between a hardware module's performance and resource

requirements. To facilitate hardware design space

exploration, we describe Aetherling, a system for

automatically compiling data-parallel programs into

statically scheduled, streaming hardware circuits.

Aetherling contributes a space- and time-aware

intermediate language featuring data-parallel

operators that represent parallel or sequential

hardware modules, and sequence data types that

encode a module's throughput by specifying when

sequence elements are produced or consumed. As a

result, well-typed operator composition in the

space-time language corresponds to connecting

hardware modules via statically scheduled, streaming

interfaces.

We provide rules for transforming programs written

in a standard data-parallel language (that carries

no information about hardware implementation)

into equivalent space-time language programs. We

then provide a scheduling algorithm that searches

over the space of transformations to quickly

generate area-efficient hardware designs that

achieve a programmer-specified throughput. Using

benchmarks from the image processing domain, we

demonstrate that Aetherling enables rapid exploration of

hardware designs with different throughput and area

characteristics, and yields results that require

1.8-7.9x fewer FPGA slices than those of

prior hardware generation systems.